I’m writing in the hope that someone with more PureData experience and expertise than me (which would be >98% PureData users!) might have the time & inclination to give a patch a once-over and make a few comments.

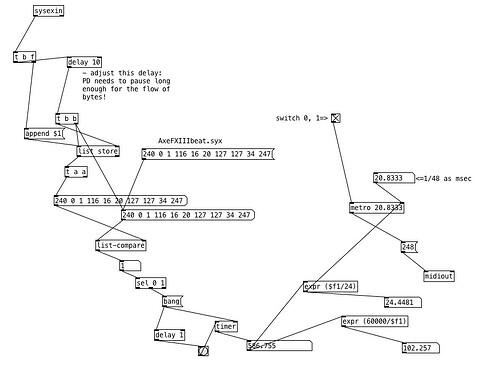

this is the diagram of the first rough working draft

if you might be interested here's more details

Its flow is pretty basic:

-

take a

sysexin(entering ‘on the beat’) -

store it in a list

-

compare to a list constant

(the ‘Beat Sysex’ is alwaysF0 00 01 74 10 14 7F 7F 22 F7) -

if it matches, read from a

timer,

then reset it for the next ‘Beat Sysex’ -

use the

timerreading to calibrate ametro, which -

triggers sending of

F8Clock messages out

all the component are lifted from other peoples’ work; my main contribution is fumbling around trying to makes the right connections.

(I’m still on the very start of the learning curve!)

If you think you can give it some time, I’d happy to add patch comments specifying my queries and next stages –eg. loadbang-start the metro with default 120BPM – as well as a zip with the abstractions (all just from list-abs).

I’d ultimately like to get this standalone as a boot patch on someone else’s rPi. (Which is why I wanna get it right!)

Thanks!